# Analysis of Signal Integrity in High-Speed Digital IC's, by Combining MOSFET Modeling and the LE-FDTD Method

F. Alimenti<sup>1</sup>, G. Stoppioni<sup>1</sup>, P. Placidi<sup>1</sup>, P. Ciampolini<sup>2</sup>, L. Roselli<sup>1</sup>, R. Sorrentino<sup>1</sup>

<sup>1</sup>Dipartimento di Ingegneria Elettronica e dell'Informazione, Università di Perugia, via G. Duranti 93, 06125 Perugia, Italy.

<sup>2</sup>Dipartimento di Ingegneria dell'Informazione, Università di Parma, Parco Area delle Scienze 181/A, 43100 Parma, Italy.

**Abstract**— For the reliable design of high-speed digital integrated circuits, signal integrity analysis of the critical interconnection lines need to be performed. Such an analysis should account for electromagnetic effects (propagation, impedance mismatch, cross-talk and substrate losses) as well as for the nonlinear behavior of the active circuitry. This work proposes a comprehensive approach to carry-out the above analysis. In particular, an accurate MOSFET analytical model, suitable for advanced submicrometric microelectronic technologies, has been incorporated in a full-wave simulator based on the Lumped Element Finite Difference Time Domain (LE-FDTD) method. In this abstract, discretization and implementation procedures are discussed, and some preliminary simulations, aimed at validating the approach, are presented.

## I. INTRODUCTION

THE reliable design of modern, digital, high-speed integrated circuits must account for propagation effects along the lines which interconnect digital gates [1]. Technology-scaling yields faster and smaller transistors, whereas interconnecting lines does not scale in a comparably favorable fashion [2]; on the contrary, since the die-area does not necessarily scale down, interconnections length may even increase, at least on an average basis. This makes the impact of signal ringing, clock skew, cross-talk and other propagation effects much more critical on advanced VLSI circuit design than it was for previous technology generations [3].

CAD tools have been devised, aimed at evaluating propagation effects and their influence on the circuit behavior: it is customary, to this respect, to identify a subset of critical signal paths (long or tightly-coupled nets), to be analyzed in detail by means of conventional circuit-analysis tools (e.g., SPICE). Within such a context, digital gates are described by comprehensive models of MOS transistors, whereas interconnection lines, responsible of propagation effects, are described by lumped-element equivalent circuits. The quality of the simulation results is therefore closely related to the reliability of such equivalent circuits: the definition of

This work has been partially supported by CNR, under the "MADESS 2" project, and by MURST, in the framework of the PRIN 98 projects.

sensible circuit topologies and the characterization of their components represent a crucial bottleneck in the CAD design flow. Difficulties comes, in particular, from the inherently distributed nature of propagation effects, which scarcely lends itself to the rather drastic approximations (both physical and geometrical) usually implied in the formulation of equivalent-circuit SPICE models.

In this work, a different approach is proposed for the analysis of critical interconnection lines embedded into densely integrated circuits: here, electromagnetic field propagation is described on a distributed, physically-accurate basis, accounting at the same time for a sophisticated and comprehensive description of MOSFET devices. In particular, an advanced MOS model [4] (compatible with circuit simulation standards and thus sharing the same parameter set), is incorporated into a full-wave Maxwell equations solver, based on the Lumped Element Finite Difference Time Domain (LE-FDTD) method. The proposed approach hence allows for the rigorous modeling of electromagnetic effects (propagation, impedance mismatch, cross-talk, radiation and substrate losses), without the need of introducing approximated equivalent circuits, and carefully accounting for the nonlinear behavior of the digital circuits which terminate the nets.

## II. METHOD

The self-consistent solution of device equations and of full-wave, field-propagation equations is made possible by the Lumped-Element, Finite Difference Time Domain algorithm [5]: basically, it consists of a strategy aimed at coupling time- and space-discretized Maxwell's equations with non-linear, equivalent circuits describing active devices. According to the LE-FDTD method, the device equivalent-circuit is "mapped" onto a few cells of the discretization mesh exploited for the numerical solution of field equations: in the following, such a process is applied to the advanced model of MOSFET devices developed at Philips and known as level 9.02 model.

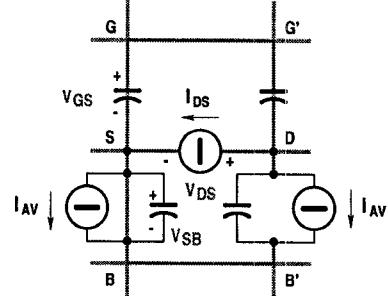

The MOS transistor model is illustrated in Fig. 1(a): it consists of the voltage-controlled drain current source and of four non-linear capacitors. Drain- and source-bulk junctions are accounted for as well, and are not

shown in figure, for the sake of clarity. Avalanche current, responsible for the drain-bulk breakdown is taken into account by the  $I_{AV}$  current source. A complete discussion of the interdependency among branch currents and node voltages and charges goes beyond the scope of this paper, and can be found in the model's reference documentation [6]: here it may be sufficient to mention that many second-order effects, typical of sub-micrometric devices (such as short- and narrow-channel effects, etc.), are accurately accounted for, resulting in a fairly complicated formulation of the device equations, which features over 80 parameters. Such parameters, in turn, can be extracted by experimental device characterization: by using, in the present context, a widely diffused SPICE-model, virtually compatible with standard circuit tools, we may rely, to this purpose, on the parameter sets usually distributed by silicon foundries. Despite its inherent intricacy, the model exhibits a simple topology, featuring a limited number of equivalent bipolar elements: each of these elements is associated to a different side of two contiguous FDTD cells.

As proposed by Sui *et al* [5], such a lumped element results in an additional current-density term  $J_\ell$ , to be included into Ampere's equation:

$$\nabla \times \mathbf{H} = \epsilon_0 \frac{\partial \mathbf{E}}{\partial t} + \mathbf{J}_\ell \quad (1)$$

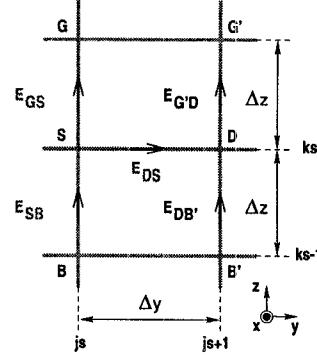

Mapping of the field components on the mesh cells, according to the Yee's notation [7], is illustrated in Fig. 1(b); for instance, assuming that the source terminal of the MOS transistor is connected to the node  $(i_s, j_s, k_s)$ , the FDTD discretization procedure yields the following update equation, for the electric field at the GS branch:

$$\begin{aligned} \mathbf{E}_{GS}^{n+1} = & \mathbf{E}_{GS}^n + \frac{\Delta t}{\epsilon_0} [\mathbf{u}_z \cdot \nabla \times \mathbf{H}]_{\mathbf{r}_{GS}}^{n+\frac{1}{2}} \\ & - \frac{1}{\epsilon_0 \Delta x \Delta y} (Q_{GS}^{n+1} - Q_{GS}^n). \end{aligned} \quad (2)$$

Here,  $\mathbf{r}_{GS} = (i_s, j_s, k_s + \frac{1}{2})$  denotes the spatial position of  $\mathbf{E}_{GS}$ ,  $\mathbf{u}_z$  the unit vector of the  $z$  axis and the expression of the discretized curl term is written in a compact form; more detailed expressions can be found in [7].

In the above equation, the charge  $Q_{GS}$  accumulated in the GS capacitor, depends, in a nonlinear fashion, on  $V_{GS}$ ,  $V_{SB}$  and  $V_{DS}$  voltages. These, in turn, can be obtained by integrating the electric field over the corresponding edges; for instance:

$$V_{GS} = -\mathbf{E}_{GS} \Delta z. \quad (3)$$

Inserting Eqs. (2) and (3) in (1) the following voltage update equation is thus obtained:

$$V_{GS}^{n+1} = A_{GS}^{n+\frac{1}{2}} +$$

(a) MOS transistor model

(b) FDTD mesh and variables

Fig. 1. FDTD compatible model of the MOS transistor. This model is composed by two voltage-controlled current generators and four nonlinear capacitors.

$$+ \frac{1}{\epsilon_0} \frac{\Delta z}{\Delta x \Delta y} Q_{GS} (V_{GS}^{n+1}, V_{SB}^{n+1}, V_{DS}^{n+1}) \quad (4)$$

In the above equation, the voltages at the time step  $n+1$  are unknown, while the term  $A_{GS}$  (which accounts for the memory of the system) is computed by using the variables computed at the previous time step:

$$\begin{aligned} A_{GS}^{n+\frac{1}{2}} = & - \frac{\Delta t \Delta z}{\epsilon_0} [\mathbf{u}_z \cdot \nabla \times \mathbf{H}]_{\mathbf{r}_{GS}}^{n+\frac{1}{2}} \\ & - \frac{1}{\epsilon_0} \frac{\Delta z}{\Delta x \Delta y} Q_{GS}^n + V_{GS}^n \end{aligned} \quad (5)$$

Similar procedures apply to the SB and DS branches, yielding:

$$\begin{aligned} V_{SB}^{n+1} = & A_{SB}^{n+\frac{1}{2}} \\ & + \frac{1}{\epsilon_0} \frac{\Delta z}{\Delta x \Delta y} Q_{SB} (V_{GS}^{n+1}, V_{SB}^{n+1}, V_{DS}^{n+1}) \end{aligned} \quad (6)$$

$$\begin{aligned} A_{SB}^{n+\frac{1}{2}} &= -\frac{\Delta t \Delta z}{\epsilon_0} [\mathbf{u}_z \cdot \nabla \times \mathbf{H}]_{\mathbf{r}_{SB}}^{n+\frac{1}{2}} \\ &- \frac{1}{\epsilon_0} \frac{\Delta z}{\Delta x \Delta y} Q_{SB}^n + V_{SB}^n \end{aligned} \quad (7)$$

and

$$\begin{aligned} V_{DS}^{n+1} &= A_{DS}^{n+\frac{1}{2}} \\ &- \frac{1}{2 \epsilon_0} \frac{\Delta t \Delta y}{\Delta x \Delta z} I_{DS} (V_{GS}^{n+1}, V_{SB}^{n+1}, V_{DS}^{n+1}) \end{aligned} \quad (8)$$

$$\begin{aligned} A_{DS}^{n+\frac{1}{2}} &= -\frac{\Delta t \Delta y}{\epsilon_0} [\mathbf{u}_y \cdot \nabla \times \mathbf{H}]_{\mathbf{r}_{DS}}^{n+\frac{1}{2}} \\ &- \frac{1}{2 \epsilon_0} \frac{\Delta t \Delta y}{\Delta x \Delta z} I_{DS}^n + V_{DS}^n \end{aligned} \quad (9)$$

for the DS branch. In Eqs. (4), (6) and (8), relationships between the quantities  $Q_{GS}$ ,  $Q_{SB}$ ,  $I_{DS}$  and the control voltages come from the Philips L9.02 model: updated voltages, in turn, are eventually used to evaluate the electric fields at the remaining cells. The resulting system of equations is solved, at each time step, by using an iterative (i.e., Newton-Raphson) algorithm: this implies a number of critical implementation issues, which cannot be exhaustively discussed in this paper, and include, to name just a few, the adaptive selection of the simulation time step, the monitoring of convergence and numerical stability, the efficient computation of the Jacobian matrix, and the control of “numerical” parasitic reactances, coming from unphysical coupling between lumped elements and field simulation domain.

### III. RESULTS

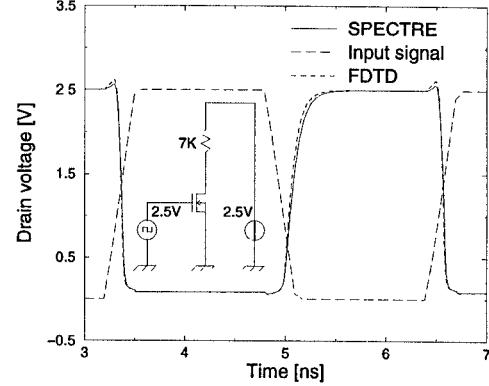

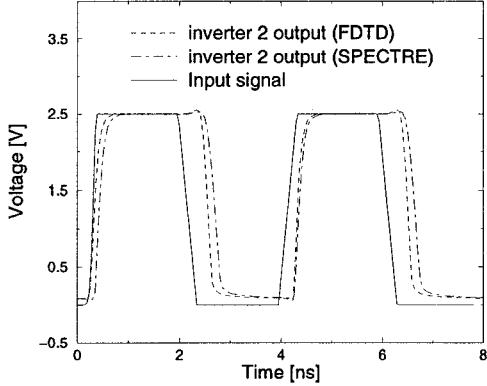

In order to validate the implementation of the MOSFET model in the LE-FDTD framework, a simple nMOS inverter has been considered, which is shown in the inset of Fig. 2. The whole circuit (including voltage sources and the load resistor) is described by lumped components, which, in turn, are embedded in a uniform FDTD mesh. The MOSFET features a  $10 \mu\text{m}$ -wide and a  $0.5 \mu\text{m}$ -long channel region; technology-dependent parameters are taken from a commercial CMOS  $0.35 \mu\text{m}$  fabrication process; a  $7\text{K}\Omega$  load is accounted for and a digital, rail-to-rail signal drives the gate, featuring  $0.3\text{ ns}$  rise and fall times. Since no significant propagation domain is accounted for in this case, LE-FDTD results can be compared with those coming from more conventional, quasi-static circuit simulators: to this purpose, the commercial tool SPECTRE has been used, which incorporates the same MOSFET compact model: matching between FDTD results and the reference data is very close, thus validating the implementation.

Fig. 2. FDTD simulated drain voltage for the simple inverter in the inset, compared with SPECTRE results.

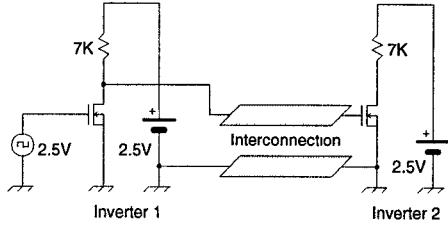

Fig. 3. Interconnection between two inverters.

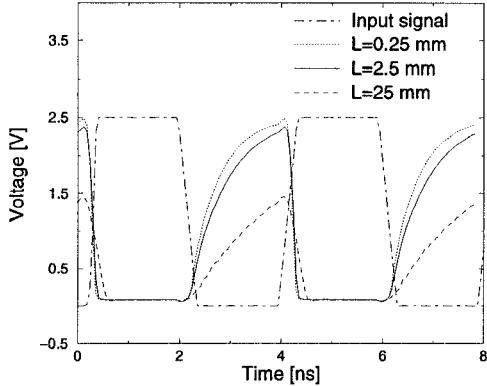

A second, more significant test has been carried out on the circuit shown in Fig. 3: here, propagation along an ideal interconnection is accounted for. A wide metal net has been considered (which exhibits an almost negligible resistance), and increasing line lengths have been taken into account (thus increasing the capacitive load). Substrate losses are not accounted for, in this case, to make comparison with SPECTRE simulation easier. A couple of inverters, identical to the one described above, act as the line driver and receiver, respectively. Propagation times at the driver stage can be estimated by looking at Fig. 5.

Rising-edge propagation is much slower than falling-edge one: this is due to the different strengths of the (passive) pull-up and (active) pull-down networks on the inverter. As the line length increases, the  $t_{pLH}$  propagation time of the driver stage increases significantly, and the waveform suffers of severe degrade. The output signal at the receiver stage, instead, is shown in Fig. 4: the noise margins of the inverter are actually large enough to recover a full-swing output-signal.

Nevertheless, the propagation delay is clearly evident. In the same figure, comparison with SPECTRE output

Fig. 4. Sensitivity to the line length for the output signal of inverter (1) of the circuit in Fig. 3.

Fig. 5. FDTD simulation of the output signal of inverter (2),  $L = 2.5$  mm in Fig. 3, compared with SPECTRE results

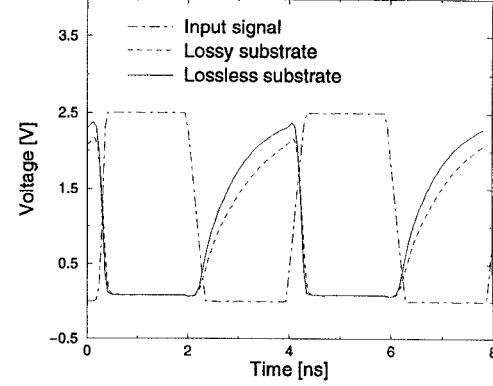

is given as well, still exhibiting a fair agreement; in the SPECTRE simulation, due to the large aspect ratio of the interconnect, the interconnect itself can be described by a bare capacitor. Finally, the same test structure has been simulated by refining the description of the physical interconnection: a  $\text{SiO}_2$  layer is assumed as the dielectric, and a lossy ( $\rho = 10^{-2} \Omega \cdot \text{cm}$ ) silicon substrate is accounted for. Simulation results for the lossy and the lossless substrate are compared in Fig. 6.

#### IV. CONCLUSIONS

A powerful simulation tool for the analysis of critical on-chip interconnections has been developed. It can self-consistently account for the nonlinear behavior of digital gates and for electromagnetic propagation effects along interconnections. Sophisticated models, suitable for the

Fig. 6. FDTD simulation of the output signal of inverter (1),  $L = 2.5$  mm in Fig. 3 considering the substrate losses.

description of submicron MOSFET devices, have been incorporated into the code. Simple validation examples have been carried-out, to illustrate the method features and to validate the proposed approach. Nevertheless, it is worth emphasizing that the method does not impose, in principle, any restriction on the interconnect geometry, and can be straightforwardly applied to the analysis of a number of cases of practical interest, such as cross-talk analysis, identification of critical paths, etc. Since the distributed approach we follow to model the E.M. field propagation is inherently computationally expensive, our tool is not actually conceived for systematic, chip-level analysis: it is to be considered, instead, in a hierarchical framework, in which detailed results coming from LE-FDTD simulation are exploited for the accurate characterization of synthetic models, to be adopted, by analysis tools placed at a higher abstraction level.

#### REFERENCES

- [1] B. Biswas et al., "Experimental electrical characterization of on-chip interconnects," in *Proc. topical meet. on el. performance of electronic packaging*, pp. 57-58, Oct. 1997.

- [2] R. H. Dennard, F. H. Gaensslen, Hwa-Nien-Yu, V. L. Rideout, E. Bassous, and A. R. LeBlanc, "Design of ion-implanted mosfet's with very small physical dimensions," *IEEE-JSCC*, vol. 9, pp. pp. 256-68, 1974.

- [3] J. K. Wee et al., "Modeling the substrate effect in interconnect line characteristics of high-speed VLSI circuits," *IEEE Trans. Microwave Theory Tech.*, vol. 46, Oct. 1998.

- [4] R. Velghe, D. Klaasen, and F. Klaasen, "Compact MOS modeling for analog circuit simulation," in *IEDM Tech. Dig.*, pp. 485-488, 1993.

- [5] W. Sui, D. Christensen, and C. Durney, "Extending the two-dimensional fd-td method to hybrid electromagnetic systems with active and passive lumped elements," *IEEE Trans. Microwave Theory Tech.*, vol. 40, pp. 724-730, 1992.

- [6] Philips-Semiconductors, "The MOS model, level 902," [www-us.semiconductors.philips.com/Philips\\_Models](http://www-us.semiconductors.philips.com/Philips_Models).

- [7] A. Taflove, *Computational electrodynamics*. Norwood, MA: Artech House Inc., 1995.